联系我们

RK3588 核心原理图(参考设计)

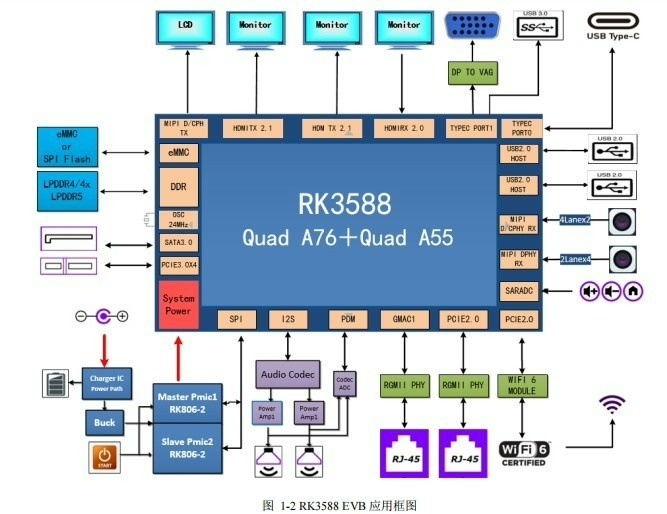

RK3588 是瑞芯微高性能 8nm 处理器,其完整原理图为商业机密,需签 NDA 获取。以下为公开参考设计的核心模块图与关键电路解析。

一、核心模块电路(官方参考)

1. 电源管理(PMIC)

核心 PMIC:RK806/RK809,提供多路核心电压

VDD_CPU/GPU:0.75V~1.1V(动态调压)

VDD_DDR:1.1V(LPDDR4/5)

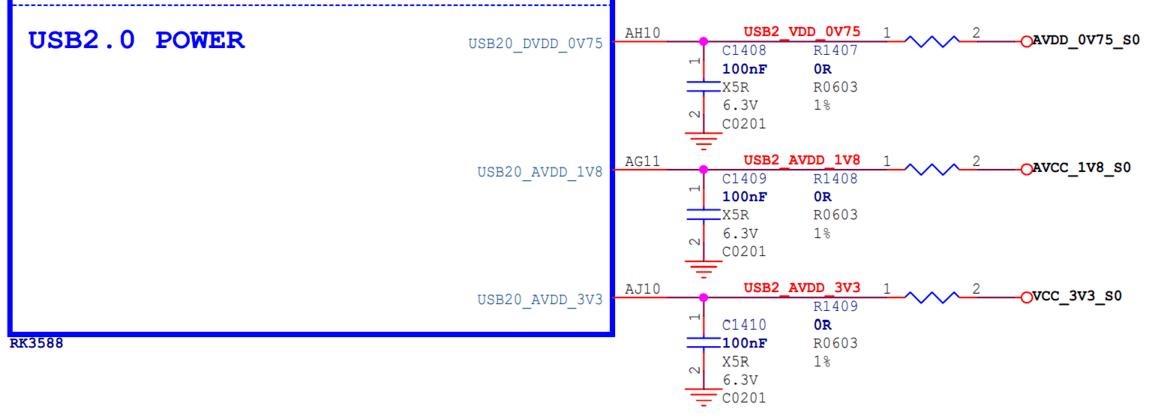

VDD_IO:1.8V/3.3V(接口供电)

电源时序:严格按VDD_CORE → VDD_DDR → VDD_IO顺序上电。

2. 时钟电路(24MHz 晶振)

核心时钟:24MHz 无源晶振(负载电容≤12pF)

电路结构:晶振→22Ω 限流电阻→RK3588XIN24M/XOUT24M

作用:提供系统主时钟,决定 CPU/GPU 工作时序。

3. DDR4/LPDDR4/5 接口

总线:32/64bit 数据位宽

关键设计:

阻抗匹配:差分线 100Ω,单端 50Ω

等长走线:误差≤5mil

电源滤波:0402 封装 10μF+0.1μF 电容。

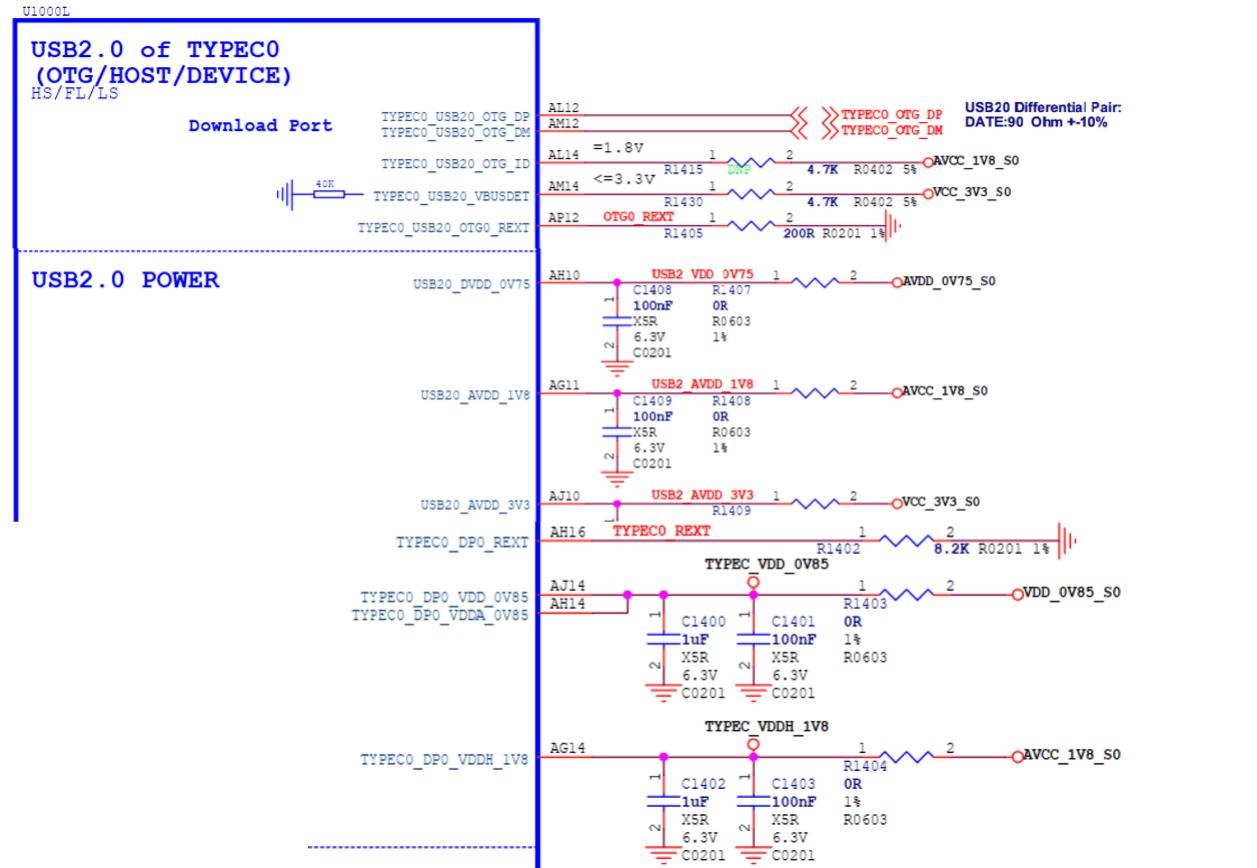

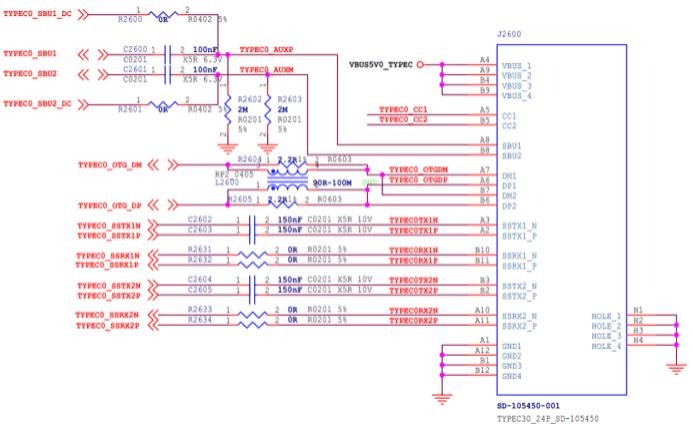

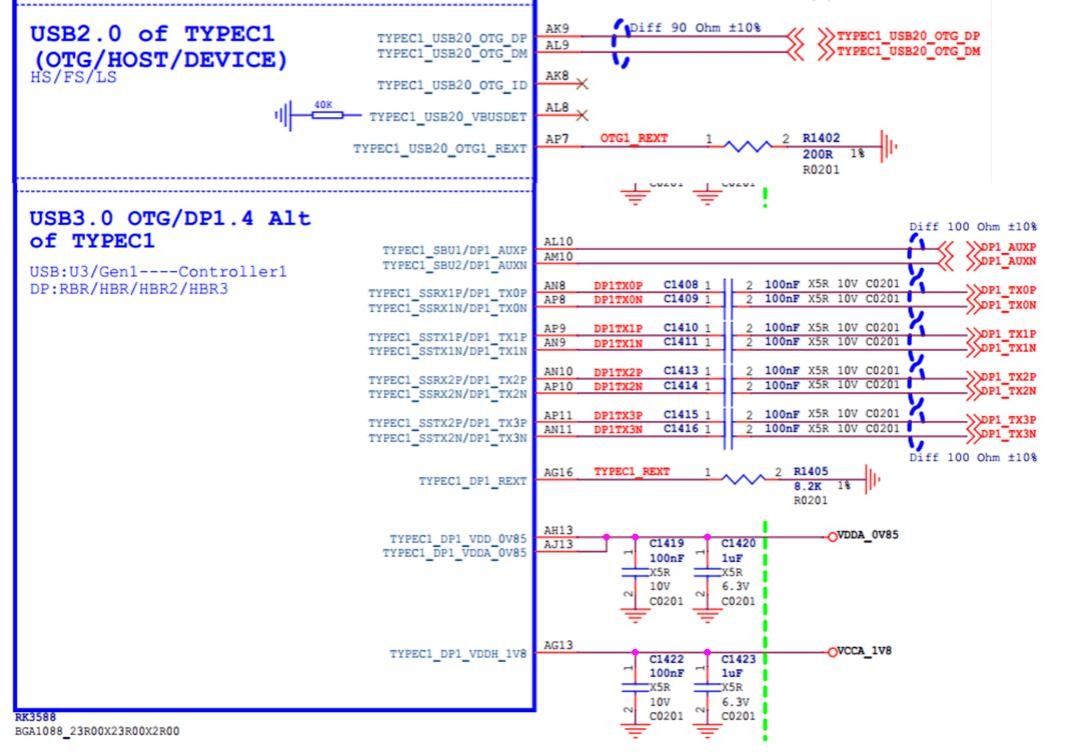

4. 高速接口(USB3.1/HDMI2.1/PCIe)

USB3.1 Type-C:支持 DP 视频输出

VBUS:5V 供电

DP0_TX/RX:高速差分信号(10Gbps)

ESD 保护:TVS 管(SMBJ6.5A)。

HDMI2.1:4K@120Hz/8K@60Hz

差分信号:TMDS_TX0~3

EDID:I2C 读取显示设备信息。

PCIe3.0:4 通道(8Gbps / 通道)

电源:3.3V/12V

复位:PERST_N(低有效)。

二、完整原理图获取途径

1. 官方渠道(需 NDA)

瑞芯微代理商 / FAE

签署保密协议后获取完整原理图(Cadence 格式)。

2. 开源开发板参考(公开)

Firefly ITX-3588J:https://github.com/Firefly-RK3588

Radxa ROCK 5B:https://github.com/radxa/rock5b

友善之臂:https://github.com/FriendlyARM/RK3588。

3. 硬件设计指南

《RK3588 Hardware Design Guide》(SDK 内置)

《RK3588 Datasheet V2.2》(官方文档)。

三、核心电路设计要点

电源:PMIC 必须支持动态调压,纹波≤50mV

DDR:严格等长、阻抗匹配、参考平面完整

高速接口:差分线走内层,避免过孔,ESD 保护

时钟:晶振靠近芯片,减少干扰。

四、原理图工具与格式

软件:Cadence Allegro、OrCAD、Altium Designer

格式:.sch(原理图)、.brd(PCB)、.pdf(导出)。

五、学习资源

官方文档:RK3588 Datasheet、Hardware Design Guide

开源项目:GitHub RK3588 开发板项目

教程:CSDN、电子发烧友网(RK3588 硬件设计实战)。

六、总结

完整原理图:需 NDA,官方提供

参考设计:开源开发板可获取核心电路

设计关键:电源时序、DDR 等长、高速接口信号完整性。

需求留言:

需求留言: