联系我们

边缘计算正迎来算力需求的井喷期,工业视觉检测、智能交通、智慧城市等场景对实时性与 AI 处理能力的要求日益严苛。然而,边缘设备的物理空间有限、散热条件苛刻、供电能力受限,传统板级拼装的异构方案(如 CPU + 独立 GPU 卡)已难以平衡算力与功耗,陷入 "算力提升 = 功耗倍增" 的困境。芯片级异构技术的崛起,为边缘智能服务器提供了破解这一矛盾的关键钥匙。

一、边缘智能的 "阿喀琉斯之踵":算力与功耗的尖锐矛盾

边缘智能服务器面临三大核心挑战,形成难以调和的三角困境:

挑战维度 | 具体表现 | 传统方案的局限 |

算力需求激增 | AI 模型参数从百万级跃升至数十亿级,4K/8K 视频流、高精度传感器数据并行处理需求大增 | 板级堆叠加速卡导致功耗与体积同步增长,超出边缘环境承载能力 |

功耗约束严苛 | 工业现场、户外基站等场景供电不稳定,嵌入式设备散热能力不足,PUE 要求趋近于 1 | 通用 CPU 处理 AI 任务能效比低,独立加速卡间通信开销大,整体能效比仅为 0.5-1TOPS/W |

混合负载复杂 | 边缘设备需同时处理实时控制、数据采集、AI 推理、协议转换等多样化任务 | 跨芯片协同延迟高,不确定性放大系统风险,难以满足毫秒级响应要求 |

某工业互联网平台数据显示,传统边缘服务器处理 10 路高清视频 AI 分析时,功耗达 300W 以上,而采用芯片级异构方案后,相同算力下功耗可降至 80W 以下,能效比提升近 4 倍。

二、芯片级异构:边缘智能的 "算力重构术"

芯片级异构(SoC 级异构)是指在单一芯片内集成多种不同架构、不同制程的计算单元(CPU、GPU、NPU、DSP、FPGA 等),通过片上网络(NoC)实现低延迟、高带宽的内部通信,配合智能调度系统实现任务的最优分配。

1. 核心技术原理:从 "各自为战" 到 "协同作战"

芯片级异构实现了三大关键突破:

架构融合:将通用计算(CPU)、并行计算(GPU)、AI 推理(NPU)、信号处理(DSP)等功能单元集成于同一芯片,避免板级通信的功耗与延迟开销;

制程混搭:采用 "芯粒(Chiplet)+ 混合键合" 技术,7nm 先进制程用于高性能计算单元,14nm 成熟制程用于 I/O 与控制单元,平衡性能与成本;

智能调度:内置硬件调度器,可在微秒级内完成任务类型识别与最优计算单元匹配,实现 "专用任务专用芯";

2. 三大技术路径:从集成到创新

技术路径 | 代表方案 | 核心优势 | 能效比提升 |

SoC 集成异构 | AMD P100 系列、华为昇腾 310、瑞芯微 RK3588 | 单芯片一体化设计,片内通信带宽达 TB/s 级,延迟降至纳秒级 | 3-5 倍 |

芯粒异构集成 | Intel Foveros、台积电 CoWoS、AMD Infinity Fabric | 模块化设计,不同功能芯粒可独立升级,良率更高 | 2-4 倍 |

存算一体异构 | MIT 3D 堆叠计算单元、三星 HBM-PIM | 数据无需搬运至内存,直接在存储单元内计算,降低 90% 数据传输能耗 | 5-10 倍 |

三、破解矛盾的关键:四大技术手段实现能效跃升

芯片级异构通过硬件创新与软件优化的深度协同,从根源上解决算力功耗矛盾:

1. 任务精准分流:专用算力单元的 "各司其职"

核心逻辑:能丢给专用单元的,绝不让 CPU 硬扛;

CPU 专注于控制流与复杂逻辑处理,保持低负载运行;

NPU 处理 AI 推理任务,通过固定算子与数据流实现极低功耗,能效比可达 100TOPS/W 以上;

GPU 负责高并行度的数据处理,如视频编解码、图像渲染;

DSP 处理传感器数据的实时滤波与信号转换;

FPGA 用于工业控制中的定制化逻辑运算,实现微秒级响应;

某智能安防案例显示,采用 NPU+CPU 的芯片级异构方案,单台服务器可处理 200 路高清视频流,功耗仅为传统 x86 服务器的 1/5,同时识别准确率提升至 99.9%。

2. 动态功耗调节:智能 "节流阀" 精准控制能耗

芯片级异构集成三大功耗管理技术,实现 "按需供能":

DVFS 动态电压频率调节:根据负载实时调整各计算单元的电压与频率,轻负载时 CPU 主频可降至 500MHz 以下,能耗降低 40% 以上;

单元级电源门控:闲置计算单元可完全断电,如 AI 推理间隙关闭 NPU 核心,减少静态功耗;

混合精度计算:自动识别任务对精度的要求,AI 推理采用 INT8/FP16 轻量化算子,算力提升 4 倍的同时功耗降低 50%;

华为昇腾 310 芯片的 "1+8+N" 异构设计中,1 个主处理核搭配 8 个能效核,在 Kaldi 语音识别任务中实现能效比提升 3.2 倍,充分体现了异构架构的优势。

3. 片上网络优化:消除数据搬运的 "功耗黑洞"

传统板级异构中,数据在 CPU、内存、加速卡间传输的能耗占系统总能耗的 30%-50%。芯片级异构通过片上网络(NoC)技术,实现三大突破:

通信带宽提升至TB/s 级别,是 PCIe 4.0 的 10 倍以上;

传输延迟从微秒级降至纳秒级,减少等待能耗;

采用 "数据就近处理" 原则,避免跨芯片数据搬运,降低 90% 数据传输能耗;

MIT 团队提出的 "3D 堆叠计算单元" 通过硅通孔(TSV)技术将内存与计算模块垂直集成,进一步将延迟从纳秒级降至皮秒级,能效比提升 5-10 倍。

4. 软硬协同优化:软件定义能效边界

芯片级异构需要软件层面的深度适配,才能发挥硬件潜力:

轻量级 AI 框架:如 TensorFlow Lite、PyTorch Mobile 针对边缘场景优化,减少内存占用与计算开销;

模型压缩技术:通过剪枝、量化、知识蒸馏,将模型体积缩小 10-100 倍,同时保持精度基本不变;

容器化部署:将不同任务封装为独立容器,实现计算资源的动态隔离与分配,提高资源利用率;

硬件抽象层:统一不同计算单元的编程接口,降低开发难度,实现 "一次开发,多单元部署";

四、实战检验:芯片级异构在边缘场景的价值爆发

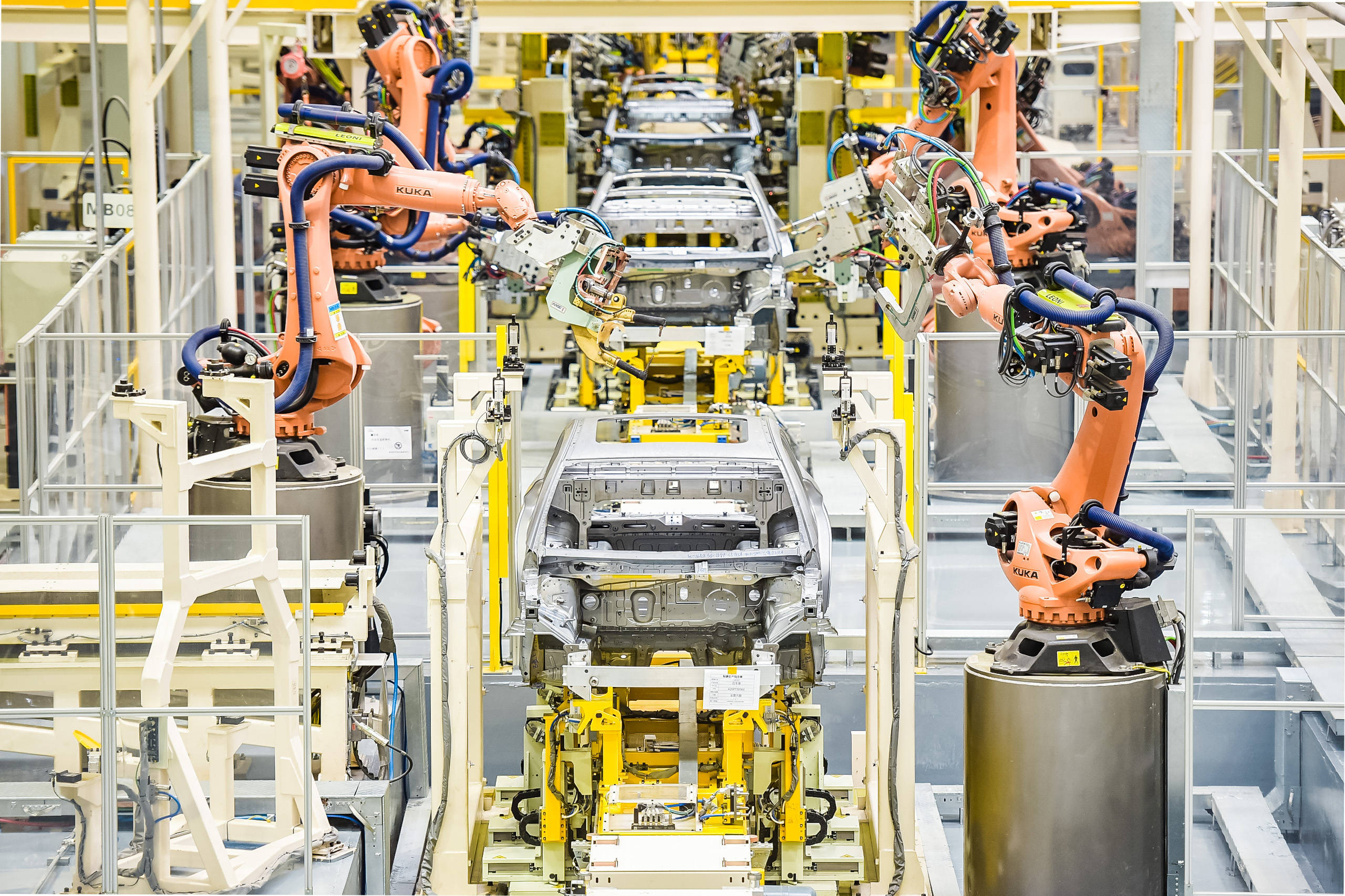

1. 智能制造:毫秒级质检与故障预测

某汽车制造企业采用 AMD P100 芯片级异构边缘服务器,实现三大突破:

产线质量检测响应时间从300ms 降至 20ms,效率提升 40%;

设备故障预测准确率达 95%,故障排查效率提升 75%;

单台服务器功耗从 250W 降至 65W,PUE 值降至 1.15;

2. 智能交通:路侧感知的能效革命

在智能高速公路场景中,芯片级异构边缘服务器实现:

同时处理 8 路 4K 视频流 + 16 路激光雷达数据,识别车辆、行人、障碍物;

功耗仅为传统方案的 1/4,支持太阳能供电,适应野外无市电环境;

端到端延迟 < 50ms,满足车路协同的实时性要求;

3. 智慧城市:边缘节点的 "算力倍增器"

某城市部署的芯片级异构边缘节点,实现:

单节点覆盖 10 个路口的交通信号控制 + 视频监控 + 流量分析;

功耗从传统方案的 180W 降至 45W,部署密度提升 3 倍;

数据本地处理率达 90%,减少 80% 核心数据外传风险;

五、未来展望:从 "平衡" 到 "超越"

芯片级异构技术正朝着三个方向演进,进一步释放边缘智能潜力:

异构集成度持续提升:从 "CPU+NPU" 二元异构到 "CPU+GPU+NPU+FPGA + 存算一体" 五元异构,覆盖更广泛的边缘应用场景;

软件定义异构加速:通过 AI 驱动的调度算法,实现计算单元的动态组合与任务的自适应分配,进一步提升能效比;

绿色能源融合:结合分布式光伏与储能系统,实现边缘节点的 "零碳运行",某试点项目显示绿电使用率已达 60%;

结语

芯片级异构技术不是简单的硬件集成,而是一场边缘计算的算力重构革命。它通过 "专用芯做专用事" 的核心理念,打破了传统边缘服务器 "算力提升必然伴随功耗激增" 的魔咒,实现了能效比的指数级提升。随着芯粒技术与混合键合工艺的成熟,芯片级异构将成为边缘智能服务器的标配,为数字经济的 "最后一公里" 提供更高效、更绿色、更可靠的算力支撑,推动边缘智能真正走向规模化普及。

需求留言:

需求留言: